## 32M x 16 Mobile DDR Synchronous DRAM (SDRAM)

#### **Etron Confidential**

**Advanced (Rev. 1.0 Mar. /2009)**

#### **Features**

Fast clock rate: 166/133 MHz

Differential Clock CK & CK

• Bi-directional DQS

• Four internal banks, 8M x 16-bit for each bank

• Edge-aligned with read data, centered in write data

• Programmable Mode and Extended Mode Registers

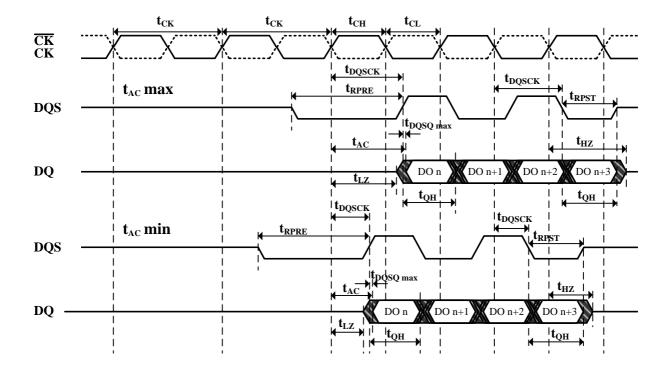

- CAS Latency: 2, or 3

- Burst length: 2, 4, 8, or 16

- Burst Type: Sequential & Interleaved

- PASR (Partial Array Self Refresh)

Auto TCSR (Temperature Compensated Self Refresh)

- DS (Drive Strength)

• Individual byte writes mask control

• DM Write Latency = 0

• Precharge Standby Current = 300 μA

• Self Refresh Current = 700 μA

• Deep power-down Current = 10 μA max. at 85

Auto Refresh and Self Refresh

• 8192 refresh cycles / 64ms

No DLL (Delay Lock Loop), to reduce power; CK to DQS is not synchronized.

• Power supplies:  $V_{DD}$  &  $V_{DDQ}$  = +1.8V+0.15V/-0.1V

• Interface: LVCMOS

• Ambient Temperature T<sub>A</sub> = -25 ~ 85 ,

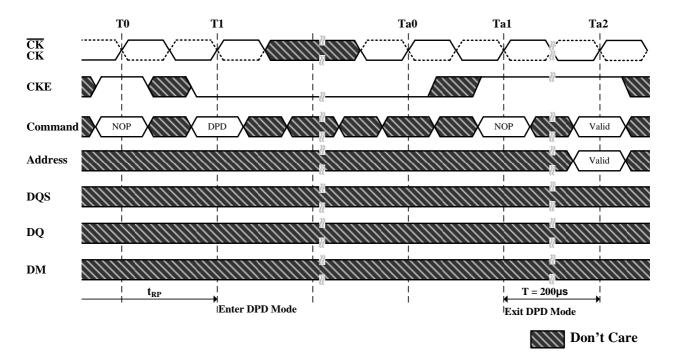

• 60-ball 8mm x 10mm VFBGA package

- Pb free and Halogen free

### Table 1. Ordering Information

| Part Number     | Clock<br>Frequency | Data Rate   | IDD6   | Package |

|-----------------|--------------------|-------------|--------|---------|

| EM68B16DVAA-6H  | 166MHz             | 333Mbps/pin | 700 μΑ | VFBGA   |

| EM68B16DVAA-75H | 133MHz             | 266Mbps/pin | 700 μΑ | VFBGA   |

VA: indicates VFBGA package

A: indicates Generation Code

H: indicates Pb and Halogen Free for VFBGA Package

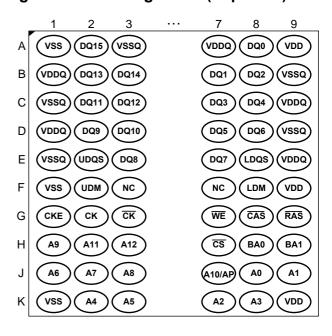

### Figure 1. Ball Assignment (Top View)

### Overview

The EM68B16D is 536,870,912 bits of double data rate synchronous DRAM organized as 4 banks of 8,388,608 words by 16 bits. The synchronous operation with Data Strobe allows extremely high performance. EM68B16D is applied to reduce leakage and refresh currents while achieving very high speed. I/O transactions are possible on both edges of the clock. The ranges of operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

## Etron Technology, Inc.

No. 6, Technology Rd. V, Hsinchu Science Park, Hsinchu, Taiwan 30078, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

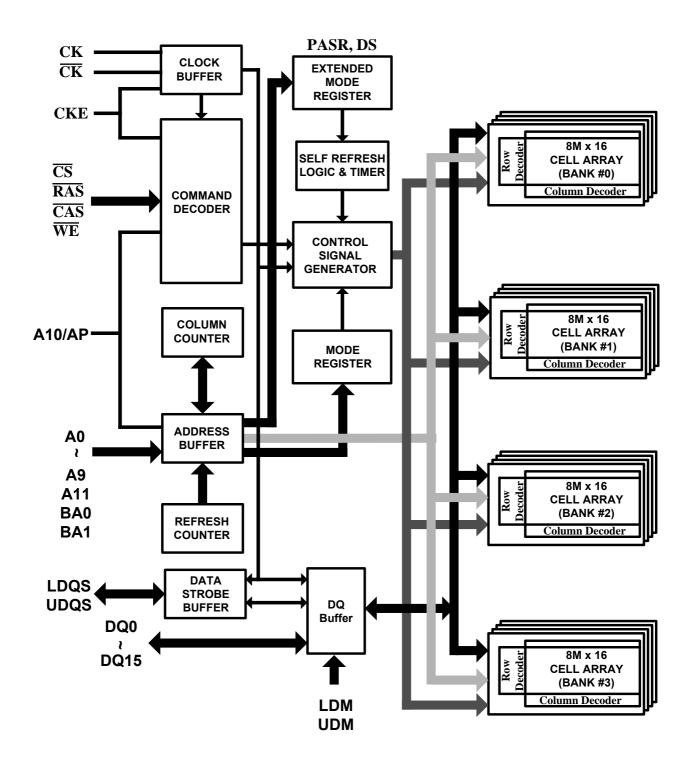

Figure 2. Block Diagram

## **Pin Descriptions**

Table 2. Pin Details of EM68B16D

| Symbol     | Type              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK     | Input             | <b>Differential Clock:</b> CK, $\overline{\text{CK}}$ are driven by the system clock. All SDRAM input signals are sampled on the positive edge of CK. Both CK and $\overline{\text{CK}}$ increment the internal burst counter and controls the output registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CKE        | Input             | Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CK signal. Internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power Down and Self Refresh operation (all banks idle) or Active Power Down (Row Active in any bank). CKE is synchronous for all functions except for disabling outputs, which is asynchronous. Input buffers, excluding CK, $\overline{CK}$ and CKE, are disabled during Power Down and Self Refresh modes to reduce standby power consumption.                                                                                                                                                                                                              |

| BA0, BA1   | Input             | <b>Bank Activate:</b> BA0 and BA1 define to which bank the BankActivate, Read, Write, or BankPrecharge command is being applied. BA0 and BA1 also determine which mode register (MRS or EMRS) is loaded during a Mode Register Set command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A0-A12     | Input             | <b>Address Inputs:</b> A0-A12 are sampled during the BankActivate command (row address A0-A12) and Read/Write command (column address A0-A9 with A10 defining Auto Precharge).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CS         | Input             | Chip Select: $\overline{CS}$ enables (sampled LOW) and disables (sampled HIGH) the command decoder. All commands are masked when $\overline{CS}$ is sampled HIGH. $\overline{CS}$ provides for external bank selection on systems with multiple banks. It is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RAS        | Input             | <b>Row Address Strobe:</b> The $\overline{RAS}$ signal defines the operation commands in conjunction with the $\overline{CAS}$ and $\overline{WE}$ signals and is latched at the positive edges of CK. When $\overline{RAS}$ and $\overline{CS}$ are asserted "LOW" and $\overline{CAS}$ is asserted "HIGH," either the BankActivate command or the Precharge command is selected by the $\overline{WE}$ signal. When the $\overline{WE}$ is asserted "HIGH," the BankActivate command is selected and the bank designated by BA is turned on to the active state. When the $\overline{WE}$ is asserted "LOW," the Precharge command is selected and the bank designated by BA is switched to the idle state after the precharge operation. |

| CAS        | Input             | <b>Column Address Strobe:</b> The $\overline{\text{CAS}}$ signal defines the operation commands in conjunction with the $\overline{\text{RAS}}$ and $\overline{\text{WE}}$ signals and is latched at the positive edges of CK. When $\overline{\text{RAS}}$ is held "HIGH" and $\overline{\text{CS}}$ is asserted "LOW," the column access is started by asserting $\overline{\text{CAS}}$ "LOW." Then, the Read or Write command is selected by asserting $\overline{\text{WE}}$ "HIGH" or LOW"."                                                                                                                                                                                                                                          |

| WE         | Input             | Write Enable: The $\overline{\text{WE}}$ signal defines the operation commands in conjunction with the $\overline{\text{RAS}}$ and $\overline{\text{CAS}}$ signals and is latched at the positive edges of CK. The $\overline{\text{WE}}$ input is used to select the BankActivate or Precharge command and Read or Write command.                                                                                                                                                                                                                                                                                                                                                                                                          |

| LDQS, UDQS | Input /<br>Output | <b>Bidirectional Data Strobe:</b> DQS is an output with read data and an input with write data. DQS is edge-aligned with read data, centered in write data. It is used to capture data. For x16, LDQS is DQS for DQ0-DQ7 and UDQS is DQS for DQ8-DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Etron Confidential 3 Rev. 1.0 Mar. 2009

| LDM, UDM         | Input             | <b>Data Input Mask:</b> DM is an input mask signal for write data. Input data is masked when DM is sampled High along with input data during a Write access. DM is sampled on both edges of DQS. DM pins include dummy parasitic loading internally to match the DQ and DQS loading. For x16, LDM is DM for DQ0-DQ7 and UDM is DM for DQ8-DQ15. |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ0 - DQ15       | Input /<br>Output | <b>Data I/O:</b> The DQ0-DQ15 input and output data are synchronized with the positive edges of CK and $\overline{\text{CK}}$ . The I/Os are byte-maskable during Writes.                                                                                                                                                                       |

| VDD              | Supply            | Power Supply: +1.8V+0.15V/-0.1V                                                                                                                                                                                                                                                                                                                 |

| Vss              | Supply            | Ground                                                                                                                                                                                                                                                                                                                                          |

| V <sub>DDQ</sub> | Supply            | <b>DQ Power:</b> +1.8V+0.15V/-0.1V. Provide isolated power to DQs for improved noise immunity.                                                                                                                                                                                                                                                  |

| Vssq             | Supply            | DQ Ground: Provide isolated ground to DQs for improved noise immunity.                                                                                                                                                                                                                                                                          |

| NC               | -                 | No Connect: No internal connection, these pins suggest to be left unconnected.                                                                                                                                                                                                                                                                  |

Etron Confidential 4 Rev. 1.0 Mar. 2009

### **Operation Mode**

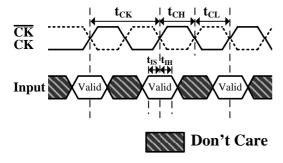

Fully synchronous operations are performed to latch the commands at the positive edges of CK. Table 3 shows the truth table for the operation commands.

Table 3. Truth Table (Note (1), (2))

| Command                    | State                 | CKEn-1 | CKEn | DM | BA1 | BA0 | A10 | A12-A11, A9-0     | CS | RAS | CAS | WE |

|----------------------------|-----------------------|--------|------|----|-----|-----|-----|-------------------|----|-----|-----|----|

| BankActivate               | Idle <sup>(3)</sup>   | Н      | Х    | Х  | V   | V   | Ro  | ow Address        | L  | L   | Н   | Н  |

| BankPrecharge              | Any                   | Н      | Х    | Χ  | V   | V   | L   | Х                 | L  | L   | Н   | L  |

| PrechargeAll               | Any                   | Н      | Х    | Χ  | Х   | Χ   | Н   | Х                 | L  | L   | Н   | L  |

| Write                      | Active <sup>(3)</sup> | Н      | Х    | ٧  | V   | V   | L   | 0.1               | L  | Н   | L   | L  |

| Write and AutoPrecharge    | Active <sup>(3)</sup> | Η      | Χ    | ٧  | V   | V   | Η   | Column<br>Address | L  | Н   | L   | L  |

| Read                       | Active <sup>(3)</sup> | Н      | Χ    | Χ  | V   | V   | L   | A0~A9             | L  | Η   | L   | Н  |

| Read and Autoprecharge     | Active <sup>(3)</sup> | Η      | Χ    | Χ  | V   | V   | Н   | 710 710           | L  | Н   | L   | Н  |

| Mode Register Set          | ldle                  | Н      | Х    | Χ  | L   | L   |     | OP code           | L  | L   | L   | L  |

| Extended Mode Register Set | Idle                  | Н      | Х    | Χ  | Н   | L   |     | OF code           | L  | L   | L   | L  |

| No-Operation               | Any                   | Н      | Х    | Χ  | Х   | Χ   | Χ   | Х                 | L  | Н   | Н   | Н  |

| Device Deselect            | Any                   | Н      | Х    | Χ  | Х   | Χ   | Χ   | Х                 | Н  | Χ   | Х   | Х  |

| Burst Stop                 | Active <sup>(4)</sup> | Ι      | Χ    | Х  | Х   | Χ   | Χ   | Х                 | L  | Ι   | Н   | L  |

| AutoRefresh                | Idle                  | Ι      | Η    | Χ  | Χ   | Χ   | Χ   | X                 | L  | Ш   | L   | Н  |

| SelfRefresh Entry          | ldle                  | Ι      | L    | Χ  | Х   | Χ   | Χ   | Х                 | L  | ┙   | L   | Н  |

| SelfRefresh Exit           | ldle                  | L      | Н    | Х  | Х   | Х   | Х   | Χ                 | Н  | Χ   | Χ   | Χ  |

| Com ton con Exit           | (Self Refresh)        | _      |      | ,  | ,   |     | ,,  |                   | L  | Н   | Н   | Н  |

| Power Down Mode Entry      | Idle/Active(5         | Н      | L    | Х  | Х   | Х   | Х   | Х                 | Ι  | Χ   | Х   | Χ  |

| - Wei Bewii Mode Enay      | )                     |        | _    | ^  | ^   | ^   | ^   | Α                 | L  | Н   | Н   | Н  |

| Power Down Mode Exit       | Any                   | L      | Н    | Х  | Х   | Х   | Х   | Х                 | Н  | Χ   | Χ   | Х  |

| Tower Bown Mode Exit       | (Power Down)          | _      |      | ^  | ^   | ^   | ^   | ^ _ ^             |    | Н   | Н   | Н  |

| Deep Power Down Entry      | Any                   | Н      | L    | Х  | Χ   | Χ   | Χ   | Χ                 | L  | Н   | Н   | L  |

| Deep Power Down Exit       | Any                   | L      | Н    | Х  | Χ   | Х   | Х   | Χ                 | Н  | Х   | Х   | Х  |

| Data Write/Output Enable   | Active                | Н      | Χ    | L  | Χ   | Χ   | Χ   | Х                 | Χ  | Χ   | Χ   | Х  |

| Data Mask/Output Disable   | Active                | Н      | Х    | Н  | Χ   | Χ   | Χ   | Х                 | Х  | Χ   | Χ   | Х  |

- **Note:** 1. V = Valid data, X = Don't Care, L = Low level, H = High level

- 2. CKE<sub>n</sub> signal is input level when commands are provided.

- CKE<sub>n-1</sub> signal is input level one clock cycle before the commands are provided.

- 3. These are states of bank designated by BA0, BA1signals.

- 4. Read burst stop with BST command for all burst types.

- 5. Power Down Mode can not enter in the burst operation. When this command is asserted in the burst cycle, device state is clock suspend mode.

**Etron Confidential** 5 Rev. 1.0 Mar. 2009

#### **Functional Description**

This 512Mb Mobile DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits. It is internally configured as a quad-bank DRAM. Each of the 134,217,728-bit banks is organized as 8,192 rows by 1024 columns by 16 bits. The 512Mb Mobile DDR SDRAM uses a double data rate architecture to achieve high speed operation. EM68B16D is applied to reduce leakage and refresh currents while achieving very high speed. The double data rate architecture is essentially a 2n-prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O balls. Single read or write access for the 512Mb Mobile DDR SDRAM consists of a single 2n-bit wide, one-clock-cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O balls.

Read and write accesses to the Mobile DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with an Active command, which is then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select the bank and row to be accessed (BA0, BA1 select the bank, A0-A12 select the row). The address bits (BA0, BA1 select the bank, A0-A9 select the column) registered coincident with the READ or WRITE command are used to select the starting column location for the burst access.

Note that the DLL (Delay Lock Loop) circuitry used on standard DDR devices is not included in the Mobile DDR SDRAM. It has been omitted to save power.

Prior to normal operation, the Mobile DDR SDRAM must be initialized.

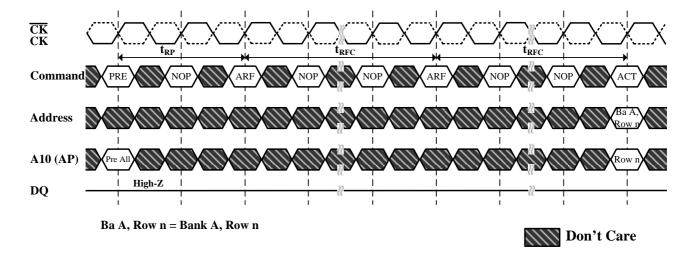

### Power-Up and Initialization

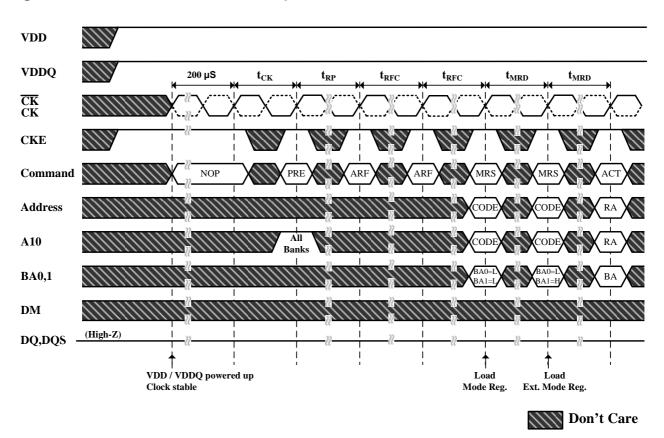

Mobile DDR SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. To properly initialize the Mobile DDR SDRAM, this sequence must be followed:

- 1. To prevent device latch-up, it is recommended that core power  $(V_{DD})$  and I/O power  $(V_{DDQ})$  be from the same power source and be brought up simultaneously. If separate power sources are used,  $V_{DD}$  must lead  $V_{DDO}$ .

- 2. Once power supply voltages are stable and CKE has been driven High, it is safe to apply the clock.

- 3. Once the clock is stable, a 200µs (minimum) delay is required by the Mobile DDR SDRAM prior to applying an executable command. During this time, NOP or Deselect commands must be issued on the command bus.

- 4. Issue a Precharge All command.

- 5. Issue NOP or Deselect commands for at least  $t_{RP}$  time.

- 6. Issue an Auto Refresh command followed by NOP or Deselect commands for at least t<sub>RFC</sub> time. Issue a second Auto Refresh command followed by NOP or Deselect commands for at least t<sub>RFC</sub> time. As part of the individualization sequence, two Auto Refresh commands must be issued. Typically, both of these commands are issued at this stage as described above. Alternately, the second Auto Refresh command and NOP or Deselect sequence can be issued between steps 10 and 11.

- 7. Using the Mode Register Set command, load the standard Mode Register as desired.

- 8. Issue NOP or Deselect commands for at least  $t_{\text{MRD}}$  time.

- 9. Using the Mode Register Set command, load the Extended Mode Register to the desired operating modes. Note that the sequence in which the standard and extended mode registers are programmed is not critical.

- 10. Issue NOP or Deselect commands for at least t<sub>MRD</sub> time.

- 11. The Mobile DDR SDRAM has been properly initialized and is ready to receive any valid command.

Etron Confidential 6 Rev. 1.0 Mar. 2009

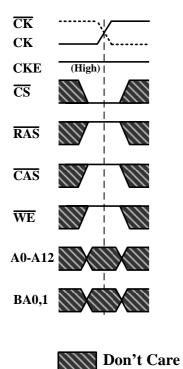

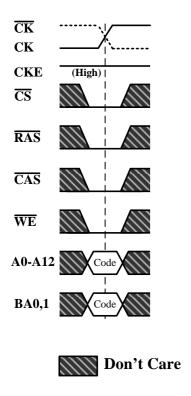

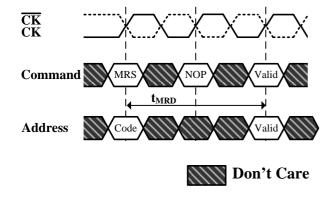

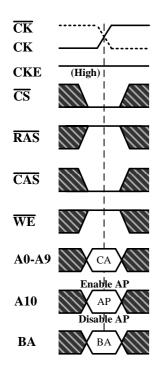

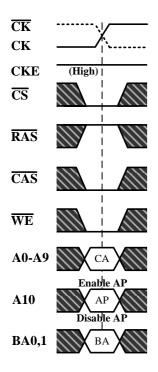

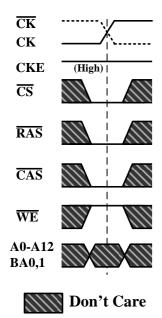

### Mode Register Set(MRS)

CK CK

Command

The Mode Register stores the data for controlling various operating modes of a DDR SDRAM. It programs  $\overline{\text{CAS}}$  Latency, Burst Type, and Burst Length to make the Mobile DDR SDRAM useful for a variety of applications. The default value of the Mode Register is not defined; therefore the Mode Register must be written by the user. Values stored in the register will be retained until the register is reprogrammed, the device enters Deep Power Down mode, or power is removed from the device. The Mode Register is written by asserting Low on  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ ,  $\overline{\text{WE}}$ , BA1 and BA0 (the device should have all banks idle with no bursts in progress prior to writing into the mode register, and CKE should be High). The state of address pins A0~A12 and BA0, BA1 in the same cycle in which  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  are asserted Low is written into the Mode Register. A minimum of two clock cycles,  $t_{\text{MRD}}$ , are required to complete the write operation in the Mode Register. The Mode Register is divided into various fields depending on functionality. The Burst Length uses A0~A2, Burst Type uses A3, and  $\overline{\text{CAS}}$  Latency (read latency from column address) uses A4~A6. A logic 0 should be programmed to all the undefined addresses to ensure future compatibility. Reserved states should not be used to avoid unknown device operation or incompatibility with future versions. Refer to the table for specific codes for various burst lengths, burst types and  $\overline{\text{CAS}}$  latencies.

|BA1|BA0|A12|A11|A10 A9 **A8** Α7 A6 Α5 A4 А3 A2 Α1 A0 | Address Field 0 0 0 0 ВТ 0 0 CAS Latency Burst Length Mode Register Α1 A6 A5 **A4** A2 A<sub>0</sub> **Burst Length CAS** Latency А3 Burst Type Reserved 0 Sequential n 0 0 0 0 0 Reserved 1 0 0 0 1 Reserved Interleave 0 1 2 4 0 1 0 0 1 0 2 0 1 3 1 8 1 0 1 0 0 1 0 0 16 1 Reserved 1 0 1 1 0 1 Reserved Reserved 1 1 0 Reserved 1 0 Reserved 1 1 1 1 1 1 Reserved Reserved

Table 4. Mode Register Bitmap

- \*1: MRS can be issued only with all banks in the idle state.

- \*2: A minimum delay of tRP is required before issuing an MRS command.

NOP

Figure 3. Mode Register Set Cycle

MRS

$t_{MRD} = 2 * t_{C}$

### **Burst Mode Operation**

Burst Mode operation is used to provide a constant flow of data to memory locations (write cycle) or from memory locations (read cycle). There are two parameters that define how the Burst Mode operates. These parameters include Burst Type and Burst Length and are programmed by addresses A0~A3 during the Mode Register Set command. Burst Type is used to define the sequence in which the burst data will be delivered from or stored to the DDR SDRAM. Two types of burst sequences are supported, Sequential and Interleaved. See the table below. The Burst Length controls the number of bits that will be output after a read command, or the number of bits to be input after a write command. The Burst Length can be programmed to have a value of 2, 4, 8, or 16.

**Table 5.Burst Definition**

| Burst  | St | art A | ddre | SS | Sequential                            | Interleave                            |

|--------|----|-------|------|----|---------------------------------------|---------------------------------------|

| Length | А3 | A2    | A1   | A0 | Sequential                            | inteneave                             |

| 2      | Χ  | Χ     | Χ    | 0  | 0,1                                   | 0,1                                   |

|        | Χ  | Χ     | Χ    | 1  | 1,0                                   | 1,0                                   |

|        | Χ  | Χ     | 0    | 0  | 0, 1, 2, 3                            | 0, 1, 2, 3                            |

| 4      | Χ  | Χ     | 0    | 1  | 1, 2, 3, 0                            | 1, 0, 3, 2                            |

| 4      | Χ  | Χ     | 1    | 0  | 2, 3, 0, 1                            | 2, 3, 0, 1                            |

|        | Χ  | Χ     | 1    | 1  | 3, 0, 1, 2                            | 3, 2, 1, 0                            |

|        | Χ  | 0     | 0    | 0  | 0, 1, 2, 3, 4, 5, 6, 7                | 0, 1, 2, 3, 4, 5, 6, 7                |

|        | Χ  | 0     | 0    | 1  | 1, 2, 3,4, 5, 6, 7, 0                 | 1, 0, 3, 2, 5, 4, 7, 6                |

|        | Χ  | 0     | 1    | 0  | 2, 3, 4, 5, 6, 7, 0, 1                | 2, 3, 0, 1, 6, 7, 4, 5                |

| 8      | Χ  | 0     | 1    | 1  | 3, 4, 5, 6, 7, 0, 1, 2                | 3, 2, 1, 0, 7, 6, 5, 4                |

| 8      | Χ  | 1     | 0    | 0  | 4, 5, 6, 7, 0, 1, 2, 3                | 4, 5, 6, 7, 0, 1, 2, 3                |

|        | Χ  | 1     | 0    | 1  | 5, 6, 7, 0, 1, 2, 3, 4                | 5, 4, 7, 6, 1, 0, 3, 2                |

|        | Χ  | 1     | 1    | 0  | 6, 7, 0, 1, 2, 3, 4, 5                | 6, 7, 4, 5, 2, 3, 0, 1                |

|        | Χ  | 1     | 1    | 1  | 7, 0, 1, 2, 3, 4, 5, 6                | 7, 6, 5, 4, 3, 2, 1, 0                |

|        | 0  | 0     | 0    | 0  | 0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15 | 0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15 |

|        | 0  | 0     | 0    | 1  | 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,0 | 1,0,3,2,5,4,7,6,9,8,11,10,13,12,15,14 |

|        | 0  | 0     | 1    | 0  | 2,3,4,5,6,7,8,9,10,11,12,13,14,15,0,1 | 2,3,0,1,6,7,4,5,10,11,8,9,14,15,12,13 |

|        | 0  | 0     | 1    | 1  | 3,4,5,6,7,8,9,10,11,12,13,14,15,0,1,2 | 3,2,1,0,7,6,5,4,11,10,9,8,15,14,13,12 |

|        | 0  | 1     | 0    | 0  | 4,5,6,7,8,9,10,11,12,13,14,15,0,1,2,3 | 4,5,6,7,0,1,2,3,12,13,14,15,8,9,10,11 |

|        | 0  | 1     | 0    | 1  | 5,6,7,8,9,10,11,12,13,14,15,0,1,2,3,4 | 5,4,7,6,1,0,3,2,13,12,15,14,9,8,11,10 |

|        | 0  | 1     | 1    | 0  | 6,7,8,9,10,11,12,13,14,15,0,1,2,3,4,5 | 6,7,4,5,2,3,0,1,14,15,12,13,10,11,8,9 |

| 16     | 0  | 1     | 1    | 1  | 7,8,9,10,11,12,13,14,15,0,1,2,3,4,5,6 | 7,6,5,4,3,2,1,0,15,14,13,12,11,10,9,8 |

| 10     | 1  | 0     | 0    | 0  | 8,9,10,11,12,13,14,15,0,1,2,3,4,5,6,7 | 8,9,10,11,12,13,14,15,0,1,2,3,4,5,6,7 |

|        | 1  | 0     | 0    | 1  | 9,10,11,12,13,14,15,0,1,2,3,4,5,6,7,8 | 9,8,11,10,13,12,15,14,1,0,3,2,5,4,7,6 |

|        | 1  | 0     | 1    | 0  | 10,11,12,13,14,15,0,1,2,3,4,5,6,7,8,9 | 10,11,8,9,14,15,12,13,2,3,0,1,6,7,4,5 |

|        | 1  | 0     | 1    | 1  | 11,12,13,14,15,0,1,2,3,4,5,6,7,8,9,10 | 11,10,9,8,15,14,13,12,3,2,1,0,7,6,5,4 |

|        | 1  | 1     | 0    | 0  | 12,13,14,15,0,1,2,3,4,5,6,7,8,9,10,11 | 12,13,14,15,8,9,10,11,4,5,6,7,0,1,2,3 |

|        | 1  | 1     | 0    | 1  | 13,14,15,0,1,2,3,4,5,6,7,8,9,10,11,12 | 13,12,15,14,9,8,11,10,5,4,7,6,1,0,3,2 |

|        | 1  | 1     | 1    | 0  | 14,15,0,1,2,3,4,5,6,7,8,9,10,11,12,13 | 14,15,12,13,10,11,8,9,6,7,4,5,2,3,0,1 |

|        | 1  | 1     | 1    | 1  | 15,0,1,2,3,4,5,6,7,8,9,10,11,12,13,14 | 15,14,13,12,11,10,9,8,7,6,5,4,3,2,1,0 |

Etron Confidential 8 Rev. 1.0 Mar. 2009

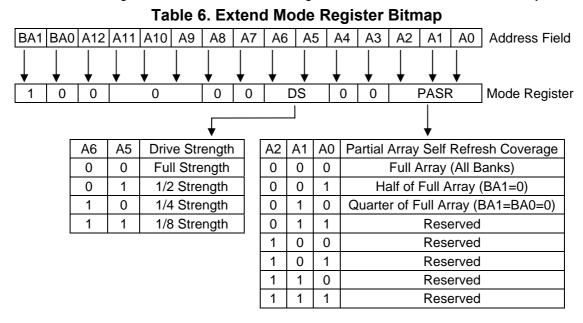

### Extended Mode Register Set (EMRS)

The Extended Mode Register is designed to support Partial Array Self Refresh and Driver Strength. The EMRS cycle is not mandatory, and the EMRS command needs to be issued only when either PASR or DS is used. The Extended Mode Register is written by asserting Low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , and BA0 and High on BA1 (the device should have all banks idle with no bursts in progress prior to writing into the Extended Mode Register, and CKE should be High). Values stored in the register will be retained until the register is reprogrammed, the device enters Deep Power Down mode, or power is removed from the device. The state of address pins A0~A12 and BA0, BA1 in the same cycle in which  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  are asserted Low is written into the Extended Mode Register. Two clock cycles,  $t_{MRD}$ , are required to complete the write operation in the Extended Mode Register. A0~A2 are used for Partial Array Self Refresh and A5~A6 are used for Driver Strength. An automatic Temperature Compensated Self Refresh function is included with a temperature sensor embedded into this device. A3~A4 are no longer used to control this function; any inputs applied to A3~A4 during EMRS are ignored. All the other address pins, A7~A12 and BA0, must be set to Low for proper EMRS operation. Refer to the tables below for specific codes. If the user does not write values to the Extended Mode Register, DS defaults to Full Strength; and PASR defaults to the Full Array.

#### TEMPERATURE COMPENSATED SELF REFRESH

In order to reduce power consumption, a Mobile DDR SDRAM includes the internal temperature sensor and other circuitry to control Self Refresh operation automatically according to two temperature ranges: max. 40°C and max. 85°C

Table 7. IDD6 Specifications and Conditions

| Tomporoturo Dongo | Self Refresh Current (IDD6) |                   |                   |      |  |  |  |

|-------------------|-----------------------------|-------------------|-------------------|------|--|--|--|

| Temperature Range | Full Array                  | 1/2 of Full Array | 1/4 of Full Array | Unit |  |  |  |

| Max. 40°C         | 490                         | 350               | 280               | μΑ   |  |  |  |

| Max. 85°C         | 700                         | 460               | 340               | μА   |  |  |  |

#### PARTIAL ARRAY SELF REFRESH

For further power savings during Self Refresh, the PASR feature allows the controller to select the amount of memory that will be refreshed during Self Refresh. The refresh options are all banks (banks 0, 1, 2 and 3); two banks (bank 0 and 1); and one bank (bank 0). Write and Read commands can still affect any bank during standard operations, but only the selected banks will be refreshed during Self Refresh. Data in unselected banks will be lost.

Etron Confidential 9 Rev. 1.0 Mar. 2009

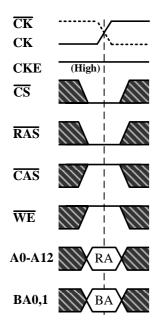

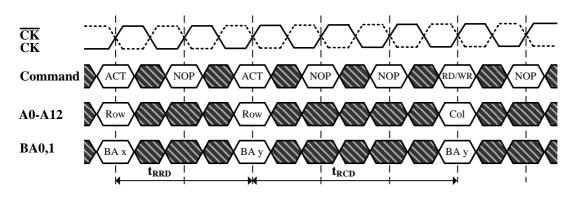

#### Bank Activation / Row Address Command

The Bank Activation / Row Address command, also called the Active command, is issued by holding  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  High with  $\overline{\text{CS}}$  and  $\overline{\text{RAS}}$  Low at the rising edge of the clock (CK). The DDR SDRAM has four independent banks, so two Bank Select Addresses (BA0, BA1) are required. The Active command must be applied before any read or write operation is executed. The delay from the Active command to the first Read or Write command must meet or exceed the minimum of  $\overline{\text{RAS}}$  to  $\overline{\text{CAS}}$  delay time ( $t_{\text{RCD}}$  min). Once a bank has been activated, it must be precharged before another Active command can be applied to the same bank. The minimum time interval between interspersed Active commands (Bank 0 to Bank 3, for example) is the bank to bank delay time ( $t_{\text{RRD}}$  min).

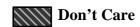

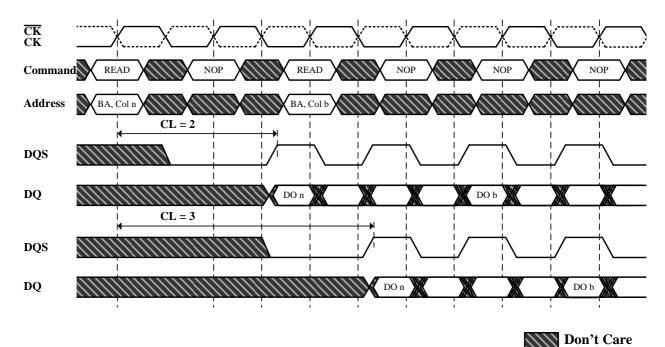

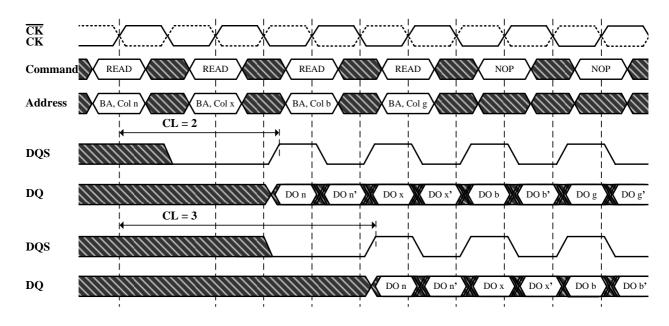

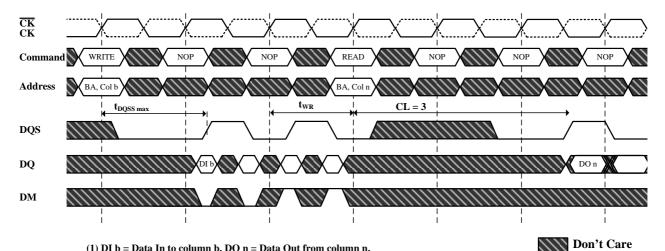

### Burst Read Operation

Burst Read operation in a DDR SDRAM is initiated by asserting  $\overline{CS}$  and  $\overline{RAS}$  Low while holding  $\overline{RAS}$  and  $\overline{WE}$  High at the rising edge of the clock (CK) after tRCD from the Active command. The address inputs (A0~A9) determine the starting address for the Burst. The Mode Register sets the type of burst (Sequential or Interleaved) and the burst length (2, 4, 8, or 16). The first output data is available after the  $\overline{CAS}$  Latency from the Read command, and the consecutive data bits are presented on the falling and rising edges of Data Strobe (DQS) as supplied by the DDR SDRAM until the burst is completed.

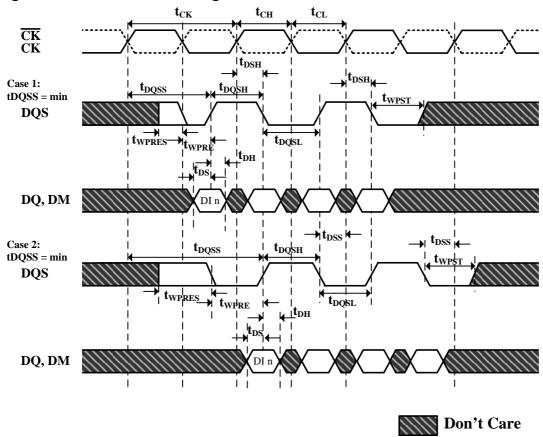

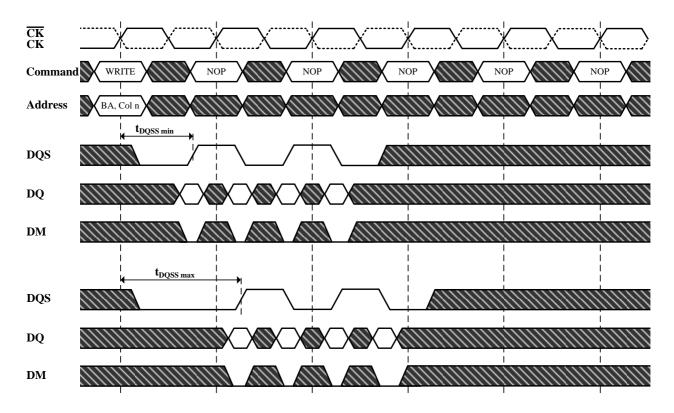

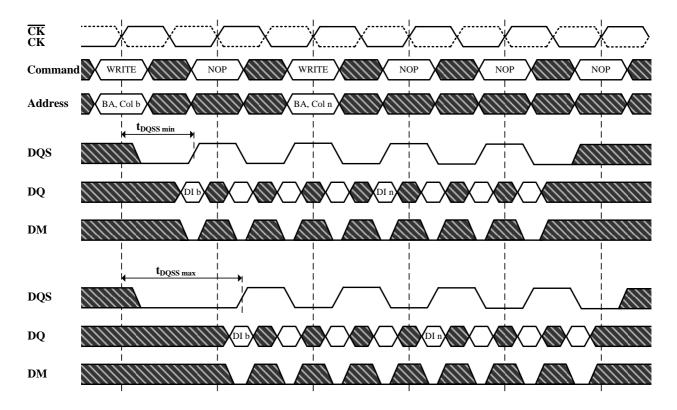

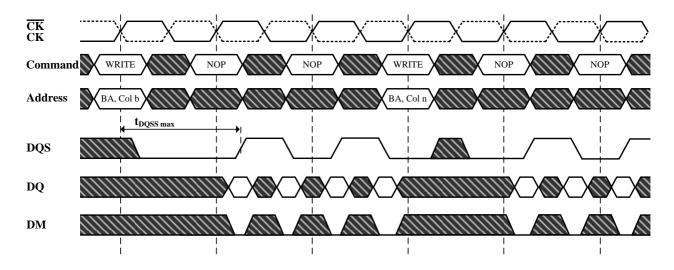

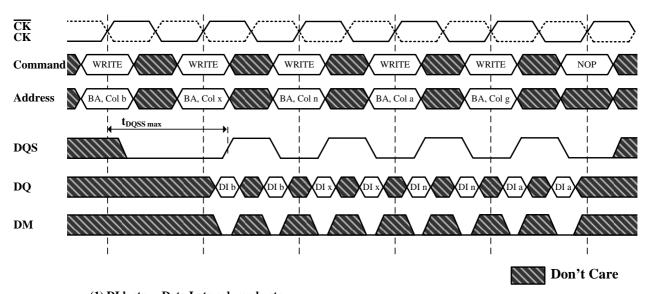

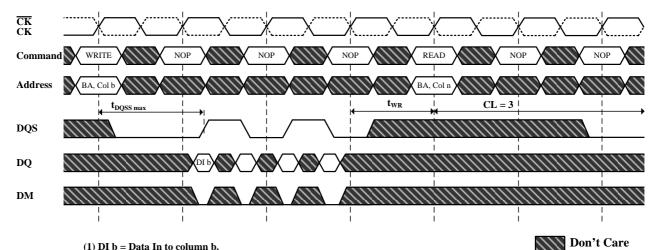

### Burst Write Operation

The Burst Write command is issued by having  $\overline{\text{CS}}$ ,  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  Low while holding  $\overline{\text{RAS}}$  High at the rising edge of the clock (CK). The address inputs determine the starting column address. There is no write latency relative to DQS required for the Burst Write cycle. The first data for a Burst Write cycle must be applied at the first rising edge of the data strobe enabled after those from the rising edge of the clock when the Write command was issued. The remaining data inputs must be supplied on each subsequent falling and rising edge of Data Strobe until the burst length is completed. After the burst has finished, any additional data supplied to the DQ pins will be ignored.

#### Burst Interruption

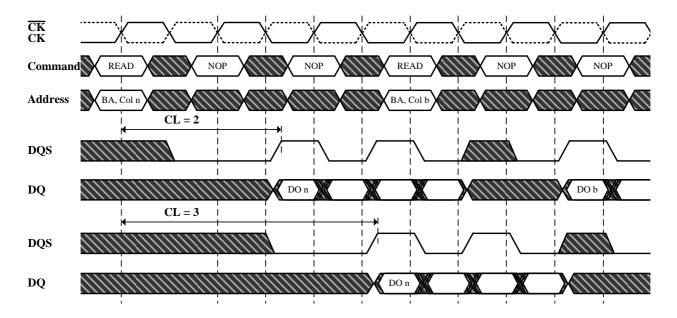

### Read Interrupted by Read

Burst Read can be interrupted before completion of the burst by a new Read command to any bank. When the previous burst is interrupted, data bits from the remaining addresses are overridden by data from the new addresses with the full burst length. The data from the previous Read command continues to appear on the outputs until the  $\overline{\text{CAS}}$  latency from the interrupting Read command is satisfied. At this point the data from the interrupting Read command appears. The Read to Read interval is a minimum of 1 clock.

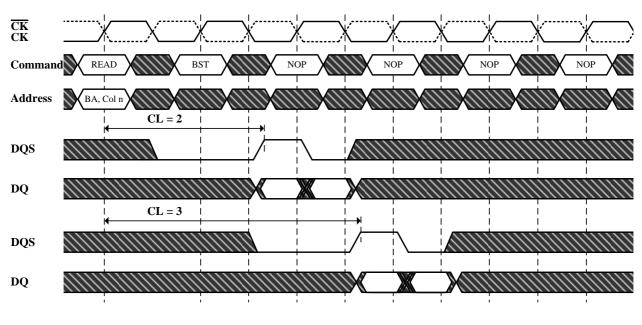

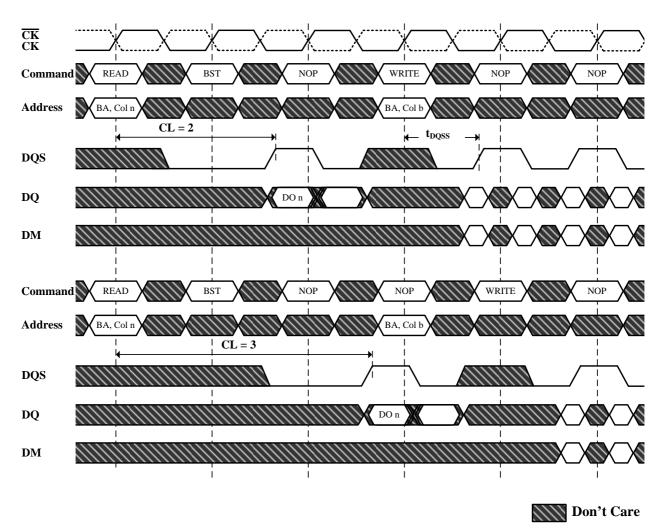

### Read Interrupted by Burst Stop & Write

To interrupt Burst Read with a write command, the Burst Stop command must be asserted to avoid data contention on the I/O bus by placing the DQ (output drivers) in a high impedance state. To ensure the DQ are tri-stated one cycle before the beginning of the write operation, the Burst Stop command must be applied at least 2 clock cycles for CL = 2 and at least 3 clock cycles for CL = 3 before the Write command.

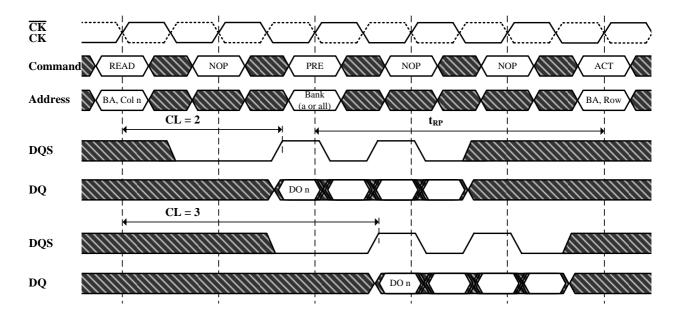

#### Read Interrupted by Precharge

Burst Read can be interrupted by a Precharge of the same bank. A minimum of 1 clock cycle is required for the read precharge interval. A Precharge command to output disable latency is equivalent to the  $\overline{CAS}$  latency.

Etron Confidential 10 Rev. 1.0 Mar. 2009

### Write Interrupted by Write

A Burst Write can be interrupted by the new Write command before completion of the previous Burst Write, with the only restriction being that the interval that separates the commands must be at least one clock cycle. When the previous burst is interrupted, the remaining addresses are overridden by the new addresses and the new data will be written into the device until the programmed Burst Length is satisfied.

### Write Interrupted by Read & DM

A Burst Write can be interrupted by a Read command to any bank. The DQ must be in the high impedance state at least one clock cycle before the interrupting read data appears on the outputs to avoid data contention. When the Read command is to be asserted, any residual data from the Burst Write sequence must be masked by DM. The delay from the last data to the Read command ( $t_{WTR}$ ) is required to avoid data contention inside the DRAM. Data presented on the DQ pins before the Read command is initiated will actually be written to the memory. A Read command interrupting a write sequence can not be issued at the next clock edge following the Write command.

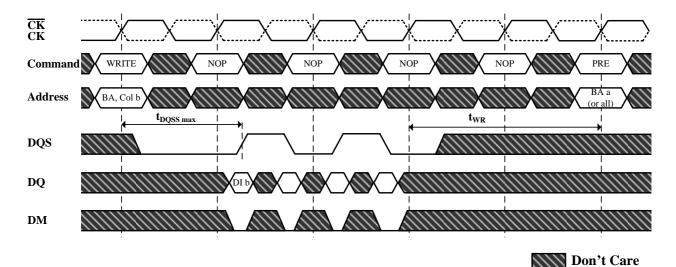

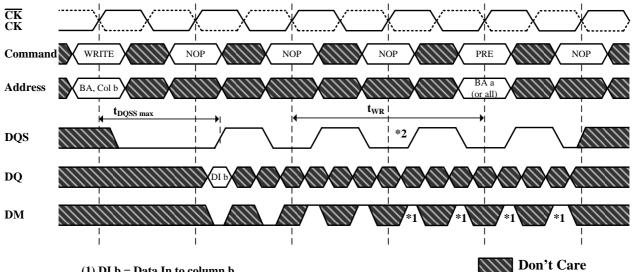

### Write Interrupted by Precharge & DM

A Burst Write can be interrupted by a Precharge of the same bank before completion of the previous burst. A write recovery time ( $t_{WR}$ ) is required from the last data to the Precharge command. When the Precharge command is asserted, any residual data from the Burst Write cycle must be masked by DM.

### Burst Stop Command

The Burst Stop command is initiated by having  $\overline{RAS}$  and  $\overline{CAS}$  High with  $\overline{CS}$  and  $\overline{WE}$  Low at the rising edge of the clock only. The Burst Stop command has the fewest restrictions, making it the easiest method to use when terminating a burst operation before it has been completed. When the Burst Stop command is issued during a Burst Read cycle, both the data and DQS (Data Strobe) go to a high impedance state after a delay which is equal to the  $\overline{CAS}$  latency set in the Mode Register. The Burst Stop command, however, is not supported during a Burst Write operation.

#### DM Masking Function

The DDR SDRAM has a Data Mask function that can be used in conjunction with the data write cycle only, not the read cycle. When the Data Mask is activated (DM High) during a write operation, the write data is masked immediately (DM to Data Mask latency is zero). DM must be issued at the rising edge or the falling edge of Data Strobe instead of at a clock edge.

### Auto Precharge Operation

Auto Precharge is a feature which performs the same individual bank precharge function as described above, but without requiring an explicit command. This is accomplished by using A10 (A10 = High), to enable Auto Precharge in conjunction with a specific READ or WRITE command. A precharge of the bank / row that is addressed with the READ or WRITE command is automatically performed upon completion of the read or write burst. Auto Precharge is non persistent in that it is either enabled or disabled for each individual READ or WRITE command. Auto Precharge ensures that a precharge is initiated at the earliest valid stage within a burst. The user must not issue another command to the same bank until the precharging time ( $t_{RP}$ ) is completed. When the Auto Precharge command is activated, the active bank automatically begins to precharge at the earliest possible moment during a read or write cycle after  $t_{RAS}$  (min) is satisfied.

### Precharge Command

The Precharge command is issued when  $\overline{CS}$ ,  $\overline{RAS}$ , and  $\overline{WE}$  are Low and  $\overline{CAS}$  is High at the rising edge of the clock (CK). The Precharge command can be used to precharge any bank individually or all banks simultaneously. The Bank Select addresses (BA0, BA1) are used to define which bank is precharged when the command is initiated. For a write cycle,  $t_{WR}$  (min) must be satisfied from the start of the last Burst Write cycle until the Precharge command can be issued. After  $t_{RP}$  from the precharge, an Active command to the same bank can be initiated.

Etron Confidential 11 Rev. 1.0 Mar. 2009

#### Auto Refresh

An Auto Refresh command is issued by having  $\overline{CS}$ ,  $\overline{RAS}$ , and  $\overline{CAS}$  held Low with CKE and  $\overline{WE}$  High at the rising edge of the clock (CK). All banks must be precharged and idle for a tRP (min) before the Auto Refresh command is applied. The refresh addressing is generated by the internal refresh address counter. This makes the address bits "Don't Care" during an Auto Refresh command. When the refresh cycle is complete, all banks will be in the idle state. A delay between the Auto Refresh command and the next Active command or subsequent Auto Refresh command must be greater than or equal to the  $t_{RFC}$  (min).

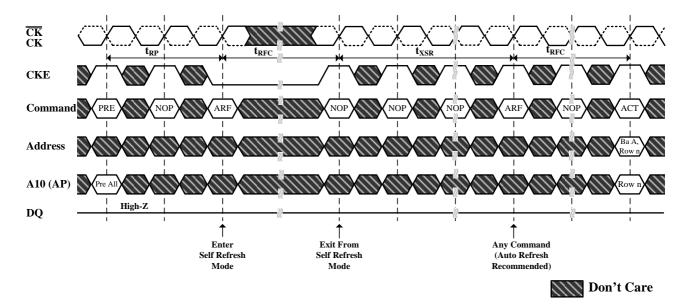

#### Self Refresh

A Self Refresh command is defined by having  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and CKE Low with  $\overline{WE}$  High at the rising edge of the clock (CK). Once the Self Refresh command has been initiated, CKE must be held Low to keep the device in Self Refresh mode. During the Self Refresh operation, all inputs except CKE are ignored. The clock is internally disabled during Self Refresh operation to reduce power consumption. To exit the Self Refresh mode, supply a stable clock input before returning CKE high, assert Deselect or a NOP command, and then assert CKE high.

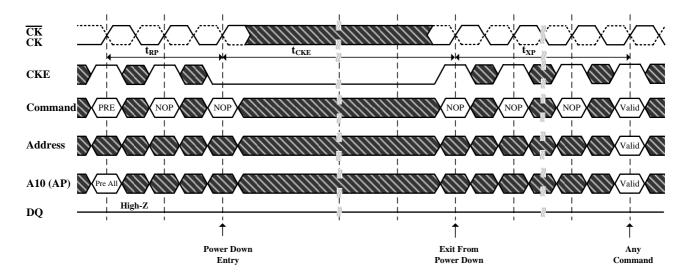

#### Power Down Mode

The device enters Power Down mode when CKE is brought Low, and it exits when CKE returns High. Once the Power Down mode is initiated, all of the receiver circuits except CK and CKE are gated off to reduce power consumption. All banks should be in an idle state prior to entering the Precharge Power Down mode and CKE should be set high at least  $t_{XP}$  prior to an Active command. During Power Down mode, refresh operations cannot be performed; therefore the device must remain in Power Down mode for a shorter time than the refresh period ( $t_{REF}$ ) of the device.

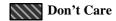

### Deep Power Down

Deep Power Down achieves maximum power reduction by eliminating the power of the whole memory array and surrounding circuitry. Data will not be retained in the memory storage array, the Mode Register, or the Extended Mode Register once the device enters Deep Power Down mode.

This mode is entered by having all banks idle then  $\overline{\text{CS}}$  and  $\overline{\text{WE}}$  held Low with  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  held High at the rising edge of the clock, while CKE is Low. This mode is exited by asserting CKE High, applying only NOP commands for 200 microseconds, and then continuing with steps 4 through 11 of the Power Up and Initialization sequence..

Etron Confidential 12 Rev. 1.0 Mar. 2009

**Table 8. Absolute Maximum Rating**

| Symbol                             | Parameter                    | Rating<br>-6/75 | Unit |

|------------------------------------|------------------------------|-----------------|------|

| VIN, VOUT                          | I/O Pins Voltage             | -0.5~2.7        | V    |

| V <sub>DD</sub> , V <sub>DDQ</sub> | Power Supply Voltage         | -0.5~2.7        | V    |

| TA                                 | Ambient Temperature          | -25~85          | °C   |

| T <sub>STG</sub>                   | Storage Temperature          | - 55~150        | °C   |

| PD                                 | Power Dissipation            | 0.7             | W    |

| Іоит                               | Short Circuit Output Current | 50              | mA   |

#### Note:

- 1. Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage of the devices.

- 2. All voltages are referenced to Vss.

- 3. Functional operation should be restricted to Recommended Operating Conditions.

- 4. Exposure to higher than the recommended voltages for extended periods of time could affect device reliability

Table 9. Recommended D.C. Operating Conditions (V<sub>DD</sub>=1.7V~1.95V, T<sub>A</sub> =-25~85°C)

| Parameter                             | Symbol               | Min.                   | Max.                   | Unit | Note                    |

|---------------------------------------|----------------------|------------------------|------------------------|------|-------------------------|

| Power Supply Voltage                  | V <sub>DD</sub>      | 1.7                    | 1.95                   | V    |                         |

| Power Supply Voltage (for I/O Buffer) | V <sub>DDQ</sub>     | 1.7                    | 1.95                   | V    |                         |

| Input High Voltage (DC)               | VIH (DC)             | $0.7 \times V_{DDQ}$   | VDDQ + 0.3             | V    |                         |

| Input Low Voltage (DC)                | V <sub>IL</sub> (DC) | -0.3                   | $0.3 \times V_{DDQ}$   | V    |                         |

| Input leakage current                 | lı∟                  | -2                     | 2                      | μΑ   |                         |

| Output leakage current                | loz                  | -5                     | 5                      | μΑ   |                         |

| Output High Voltage                   | Voн                  | 0.9 x V <sub>DDQ</sub> | -                      | V    | I <sub>OH</sub> =-0.1mA |

| Output Low Voltage                    | Vol                  | -                      | 0.1 x V <sub>DDQ</sub> | V    | I <sub>OL</sub> =0.1mA  |

Note: These parameters are guaranteed by design, periodically sampled and are not 100% tested.

Table 10. Capacitance ( $V_{DD}$ =1.7V~1.95V, f = 1MHz, T<sub>A</sub> = 25 °C)

| Symbol           | Parameter                                     |     | Max. | Delta | Unit |

|------------------|-----------------------------------------------|-----|------|-------|------|

| C <sub>IN1</sub> | Input Capacitance (CK, $\overline{CK}$ )      | 1.5 | 3    | 0.25  | pF   |

| C <sub>IN2</sub> | Input Capacitance (all other input-only pins) | 1.5 | 3    | 0.5   | pF   |

| CI/O             | DQ, DQS, DM Input/Output Capacitance          | 3   | 5    | 0.5   | pF   |

Note: These parameters are guaranteed by design, periodically sampled and are not 100% tested.

Etron Confidential 13 Rev. 1.0 Mar. 2009

Table 11. D.C. Characteristics (V<sub>DD</sub>=1.7V~1.95V, T<sub>A</sub> =-25~85°C)

| Downwater & Teet Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                  | Oh. a.l. | -6     | -75    | 11!4 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------|--------|------|

| Parameter & Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    | Symbol   | MAX    |        | Unit |

| Operating one bank active-precharge current:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |          |        |        |      |

| $t_{RC}=t_{RC}(min)$ ; $t_{CK}=t_{CK}(min)$ ; CKE is HIGH; $\overline{CS}$ is HIGH betwee commands; Address inputs are SWITCHING; data bus inputed to the sum of th |                    | IDD0     | 70     | 65     | mA   |

| Precharge power-down standby current:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |        |        |      |

| All banks idle, CKE is LOW; $\overline{\text{CS}}$ is HIGH, $t_{\text{CK}}$ = $t_{\text{CK}}$ (min);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    | IDD2P    | 0.3    | 0.3    | mΑ   |

| address and control inputs are SWITCHING; data bus input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s are STABLE       |          |        |        |      |

| Precharge power-down standby current with clock stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |        |        |      |

| All banks idle, CKE is LOW; $\overline{CS}$ is HIGH, CK = LOW, $\overline{CK}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    | IDD2PS   | 0.3    | 0.3    | mΑ   |

| address and control inputs are SWITCHING; data bus input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                  |          |        |        |      |

| Precharge non power-down standby current:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |          |        |        |      |

| All banks idle, CKE is HIGH; $\overline{\text{CS}}$ is HIGH, $t_{\text{CK}} = t_{\text{CK}}(\text{min})$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    | IDD2N    | 15     | 15     | mΑ   |

| address and control inputs are SWITCHING; data bus input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s are STABLE       |          |        |        |      |

| Precharge non power-down standby current with clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |          |        |        |      |

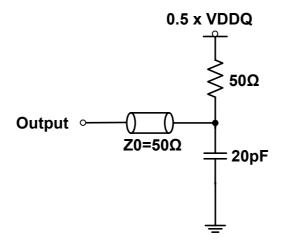

| All banks idle, CKE is HIGH; $\overline{CS}$ is HIGH, CK = LOW, $\overline{CK}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                  | IDD2NS   | 8      | 8      | mΑ   |